## SC8815 具备 I2C 控制的高效同步双向升降压充电控制器

## 1 简介

SC8815 是一款同步升降压充电控制器,同时支持电池 反向放电工作。芯片支持 VBAT 电池端 36V 高压工作, 因此在适配器电压高于、低于或者等于电池电压时,均 能保证 1-6 节锂电池应用。当工作系统需要电池提供能 量时,SC8815 也支持电池反向放电工作,输出设定的 电压,并且放电最高电压可达 36V。

用户通过 I2C 接口可以很方便地选择充电/放电模式,设置充电电流、充电电压、反向放电电压、限流值、开关频率及其它参数等。除此之外,SC8815 支持快充握手协议。集成的 10 位 ADC,可以方便用户实时检测读取VBUS/VBAT 电压和电流,使系统设计极大地简化。

SC8815 支持内部限流保护、过压保护、输出短路保护和过温保护,从而保证了各种异常情况下的安全。

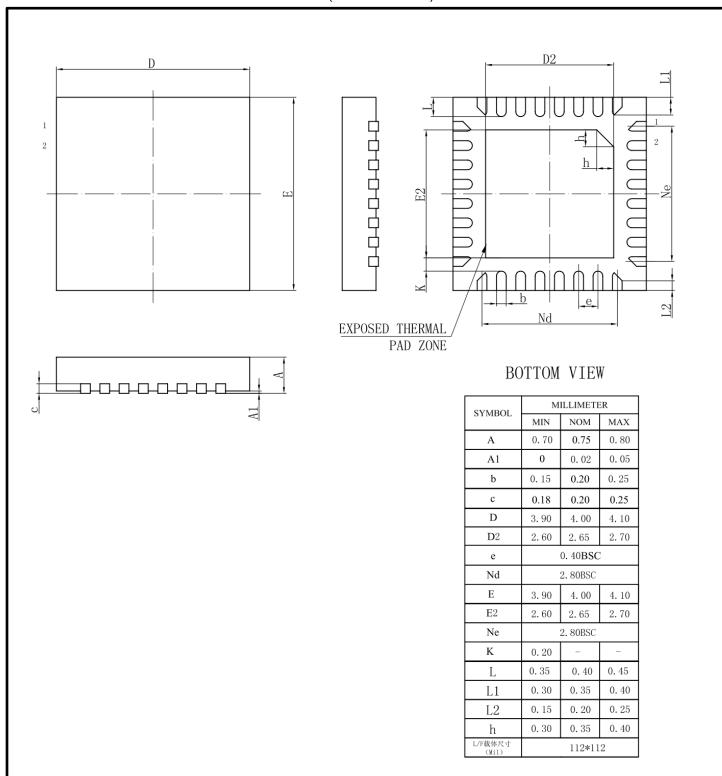

SC8815 提供 32 脚的 4x4 QFN 封装。

## 2 功能

- 支持 1-6 节电池升降压充电

- 完整的充电循环管理,包括涓流充电、恒流充电、 恒压充电和充电截止

- 反向升降压放电工作

- VBAT 宽范围: 2.7V~36V, 最高可达 40V

- VBUS 宽范围: 2.7V~36V, 最高可达 40V

- I2C 可编程控制充电电流/电压

- I2C 可编程控制反向放电电压

- 12C 可编程控制输入/输出限流

- 12C 可编程控制开关频率

- 高效率的升降压功率转换

- ▶ 内部集成 10 位 ADC

- 充电状态指示

- 事件监测:适配器接入和负载接入自动检测

- 功率路径管理

- 完善的保护:欠压保护、过压保护、过流保护、短路保护,热关断保护

- QFN-32 封装

## 3 应用

- 快充移动电源

- USB PD

- Type C Hub

- 工业电源

## 4 器件信息

| 器件号        | 封装         | 封装尺寸                   |

|------------|------------|------------------------|

| SC8815QDER | 32 pin QFN | 4.0mm x 4.0mm x 0.75mm |

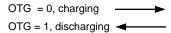

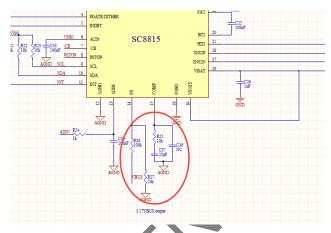

## 5 Typical Application Circuit

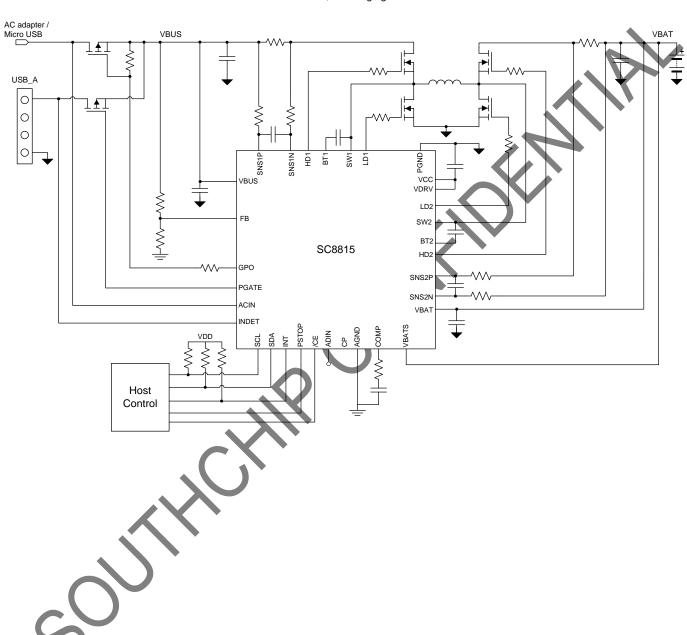

## 6 Terminal Configuration and Functions

Top View

| Т      | ERMINAL      | 1/0 | DECORPORTION                                                                                                                                                                                                                                                                              |

|--------|--------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                               |

| 1      | SNS1P        | 1   | Positive input of a current sense amplifier. Connect to one pad of the current sense resistor (typical 10 m $\Omega$ ) on the power path to sense the current into or out from VBUS.                                                                                                      |

| 2      | GPO          |     | Open drain output for general purpose. It is controlled by GPO_CTRL bit. User can use this pin to drive external PMOS with a pull up resistor.                                                                                                                                            |

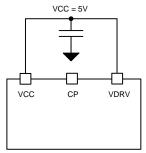

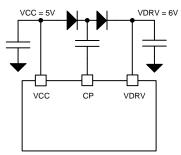

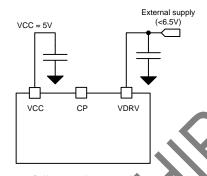

| 3      | СР           | 0   | Driver for external charge pump circuit. User can use this driver to implement a charge pump between VCC and VDRV pins to generate a 6V driving voltage at VDRV pin.                                                                                                                      |

| 4      | PGATE/DITHER | 10  | PMOS gate driver controlled by PGATE bit, used to control the external PMOS on the power path. This pin can be configured through I2C for switching frequency dithering function. Connect a ceramic capacitor (typical 100nF) from this pin to ground when for frequency dither function. |

| 5      | INDET        | I   | Connect this pin to a USB-A port to detect the load insertion event. When an insertion event is detected, the IC sets INDET bit and outputs an INT interrupt pulse to inform MCU.                                                                                                         |

| 6      | ACIN         | I   | Connect this pin to AC adapter input node or micro-USB port to detect an AC adapter insertion event. When an insertion event is detected, the IC sets AC_OK bit and outputs an INT interrupt pulse to inform MCU.                                                                         |

| 7      | /CE          | I   | Chip enable control. Pull this pin to logic low to enable the IC; pull this pin to logic high to disable the IC.  This pin is internally pulled low.                                                                                                                                      |

| 8      | PSTOP        | ı   | Power stop control. Pull this pin to logic low to enable the power blocks; pull this pin to logic high to disabled the power blocks, and the IC enters into Standby mode. In Standby mode, only the                                                                                       |

|    |       |     | AC adapter and load insert detection functions and the I2C circuits keep working.  This pin is internally pulled low.                                                                                                                                                                                                |

|----|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9  | SCL   | I   | I2C interface clock. Connect SCL to the logic rail through a pull up resistor (typical 10 k $\Omega$ ). The IC works as a slave, and the I2C address is 0x74H.                                                                                                                                                       |

| 10 | SDA   | I/O | I2C interface data. Connect SDA to the logic rail through a pull up resistor (typical 10 kΩ).                                                                                                                                                                                                                        |

| 11 | INT   | 0   | An open drain output for interrupt signal. The IC sends a logic low pulse at INT pin to inform the host if an interrupt event happens.                                                                                                                                                                               |

| 12 | AGND  | I/O | Analog ground. Connect PGND and AGND together at the thermal pad under IC.                                                                                                                                                                                                                                           |

| 13 | ADIN  | I   | ADC input pin. Apply an analog signal (≤ 2.048V) to this pin, the internal 10-bit ADC can convert this analog signal to digital signals, and store the digital values in a register.                                                                                                                                 |

| 14 | FB    | I   | Feedback node for VBUS voltage. Connect a resistor divider from VBUS to FB to set the VBUS discharging output voltage in external way. The FB reference can also be programmed through I2C.                                                                                                                          |

| 15 | COMP  | I   | Connect resistor and capacitor at this pin to compensate the control loop.                                                                                                                                                                                                                                           |

| 16 | VBATS | I   | Sense node for VBAT voltage. Connect to VBAT rail if internal way is selected for VBAT charging termination voltage setting; connect a resistor divider at VBATS external way is selected.                                                                                                                           |

| 17 | SNS2N | I   | Negative input of a current sense amplifier. Connect to one pad of the current sense resistor (typical 10 m $\Omega$ ) on the power path to sense the current into or out from battery.                                                                                                                              |

| 18 | SNS2P | I   | Positive input of a current sense amplifier. Connect to the other pad of the current sense resistor (typical 10 m $\Omega$ ) on the power path to sense the current into or out from battery.                                                                                                                        |

| 19 | VBAT  | I   | Power supply to the IC. Connect to the battery positive node. Place a 1 µF capacitor from this pin to PGND as close to the IC as possible.                                                                                                                                                                           |

| 20 | BT2   | I   | Connect a 100nF capacitor between BT2 pin and SW2 pin to bootstrap a bias voltage for high side MOSFET driver.                                                                                                                                                                                                       |

| 21 | HD2   | 0   | Gate driver output to control the external high side power MOSFET.                                                                                                                                                                                                                                                   |

| 22 | SW2   | 1/0 | Switching node. Connect to the inductor.                                                                                                                                                                                                                                                                             |

| 23 | LD2   | 0   | Gate driver output to control the external low side power MOSFET.                                                                                                                                                                                                                                                    |

| 24 | VCC   | 0   | Output of an internal 5V linear regulator. Connect a 1 $\mu F$ capacitor from VCC pin to PGND as close to the IC as possible.                                                                                                                                                                                        |

| 25 | VDRV  | I   | Power supply input for internal driver circuits. One way of getting the power supply is to connect VCC to this pin directly. Another way is to use the CP driver to implement a charge pump between VCC and VDRV pin. With the charge pump, the IC can generate maximum 6V at VDRV pin for internal driver circuits. |

| 26 | PGND  | I/O | Power ground. Connect PGND and AGND together at the PGND thermal pad under IC.                                                                                                                                                                                                                                       |

| 27 | LD1   | 0   | Gate driver output to the external low side MOSFET.                                                                                                                                                                                                                                                                  |

| 28 | SW1   | I/O | Switching Node. Connect to the inductor.                                                                                                                                                                                                                                                                             |

| 29 | HD1   | 0   | Gate driver output to the external high side MOSFET.                                                                                                                                                                                                                                                                 |

| 30 | BT1   | I   | Connect a 100nF capacitor between BT1 pin and SW1 pins to bootstrap a bias voltage for high side MOSFET driver.                                                                                                                                                                                                      |

| 31 | VBUS        | I | Power supply to the IC. Connect to the VBUS rail. Place a 1 $\mu$ F capacitor from this pin to PGND as close to the IC as possible.                                                  |

|----|-------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32 | SNS1N       | I | Negative input of a current sense amplifier. Connect to one pad of the current sense resistor (typical 10 m $\Omega$ ) on the power path to sense the current into or out from VBUS. |

| 33 | Thermal Pad |   | PGND thermal pad. Connect PGND and AGND together at the thermal pad under IC.                                                                                                        |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                     |                                                                                       | MIN                 | MAX | Unit |

|-------------------------------------|---------------------------------------------------------------------------------------|---------------------|-----|------|

| Voltage range at terminals $^{(2)}$ | CP, LD2, VCC, VDRV, LD1<br>HD1 to SW1, BT1 to SW1, BT2 to SW2, HD2 to SW2             | -0.3                | 6.5 | V    |

|                                     | PSTOP                                                                                 | LD2, VCC, VDRV, LD1 | V   |      |

|                                     | SCL, SDA, INT, ADIN, COMP                                                             | -0.3                | 5   | V    |

|                                     | FB                                                                                    | -0.3                | 30  | V    |

|                                     | VBUS, SNS1N, SNS1P, GPO, PGATE, INDET, ACIN, VBATS, SNS2N, SNS2P, VBAT, SW2, SW1, /CE | -0.3                | 40  | V    |

| terminals <sup>(2)</sup>            | VBUS to SNS1P, SNS1N                                                                  | -0.3                | 11  | V    |

|                                     | VBAT to SNS2P, SNS2N                                                                  | -0.3                | 11  | V    |

|                                     | SNS1P to SNS1N                                                                        | -10                 | 10  | V    |

|                                     | SNS2P to SNS2N                                                                        | -10                 | 10  | V    |

|                                     | BT1, HD1, BT2, HD2                                                                    | -0.3                | 45  | V    |

|                                     | BT1 to HD1, BT2 to HD2                                                                | -0.3                | 6.5 | V    |

| T <sub>J</sub>                      | Operating junction temperature range                                                  | -40                 | 150 | °C   |

| T <sub>stg</sub>                    | Storage temperature range                                                             | -65                 | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 Thermal Information

| THERMAL RESISTA | NCE <sup>(1)</sup>                     | QFN-32 (4mmX4mm) | UNIT |

|-----------------|----------------------------------------|------------------|------|

| $\theta_{JA}$   | Junction to ambient thermal resistance | 35               | °C/W |

| $\theta_{JC}$   | Junction to case resistance            | 7                | °C/W |

<sup>(1)</sup> Measured on JESD51-7, 4-layer PCB.

## 7.3 Handling Ratings

| PARAMETER          | DEFINITION                                                   | MIN  | MAX | UNIT |

|--------------------|--------------------------------------------------------------|------|-----|------|

| FCD(1)             | Human body model (HBM) ESD stress voltage <sup>(2)</sup>     | -2   | 2   | kV   |

| ESD <sup>(1)</sup> | Charged device model (CDM) ESD stress voltage <sup>(3)</sup> | -750 | 750 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

#### 7.4 Recommended Operating Conditions

|                  |                    | MIN | MAX | UNIT |

|------------------|--------------------|-----|-----|------|

| V <sub>BUS</sub> | VBUS voltage range | 2.7 | 36  | V    |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

| V <sub>BAT</sub>    | VBAT voltage range                 | 2.7 | 36  | V  |

|---------------------|------------------------------------|-----|-----|----|

| CBUS, CBAT          | VBUS Capacitance, VBAT capacitance | 30  |     | μF |

| L                   | Inductance                         | 2.2 | 10  | μH |

| R <sub>SNS1/2</sub> | Current Sensing Resistor           | 5   | 10  | mΩ |

| TA                  | Operating ambient temperature      | -40 | 85  | °C |

| TJ                  | Operating junction temperature     | -40 | 125 | °C |

## 7.5 Electrical Characteristics

$T_{J} \! = 25^{\circ} C$  and  $V_{BUS} \! = 5 V, \, V_{BAT} \! = 10.8 V$  unless otherwise noted.

| PARAMETE                 | ER                                                     | TEST CONDITIONS                                                           | MIN    | TYP    | MAX                                        | UNIT |

|--------------------------|--------------------------------------------------------|---------------------------------------------------------------------------|--------|--------|--------------------------------------------|------|

| SUPPLY VO                | DLTAGE                                                 |                                                                           |        |        |                                            |      |

| V                        | VBUS under-voltage lockout                             | Rising edge                                                               |        | 2.5    | 2.7                                        | V    |

| $V_{\text{UVLO\_VBUS}}$  | threshold                                              | Hysteresis                                                                |        | 170    | -                                          | mV   |

| M                        | VBAT under-voltage lockout                             | Rising edge                                                               |        | 2.4    | 2.6                                        | V    |

| $V_{\text{UVLO\_VBAT}}$  | threshold                                              | Hysteresis                                                                |        | 170    |                                            | mV   |

|                          |                                                        | VBUS = 5V<br>PSTOP = L, non-switching                                     |        | 2.4    | 4                                          | mA   |

| I <sub>Q_VBAT</sub>      | Quiescent current into VBAT                            | VBUS = 5V PSTOP = L, after charging termination                           |        | 2.4    | 4                                          | mA   |

| I <sub>Q_VBUS</sub>      | Quiescent current into VBUS                            | PSTOP = L, non-switching                                                  |        | 25     | 40                                         | μA   |

|                          | Standby surrent into V/DAT                             | VBUS open PSTOP = H, AD_START = 0                                         | V      | 17     | 40                                         | μА   |

| I <sub>SB_VBAT</sub>     | Standby current into VBAT                              | VBUS open PSTOP = H, AD_START = 1                                         |        | 0.65   | 1.2                                        | mA   |

| I <sub>SB_VBUS</sub>     | Standby current into VBUS                              | PSTOP = H, AD_START = 0                                                   |        | 12     | 50                                         | μA   |

| I <sub>SD_VBAT</sub>     | Shutdown current into VBAT                             | /CE = H, VBUS = open                                                      |        | 10     | 20                                         | μA   |

| VCC, DIRVI               | ER AND POWER SWITCH                                    |                                                                           |        |        |                                            |      |

| V <sub>cc</sub>          | VCC regulation voltage                                 | PSTOP = L, VBUS = 9V                                                      |        | 5.0    | 5.3                                        | V    |

|                          |                                                        | PSTOP = L, VBUS = 5V                                                      |        | 4.96   | 5                                          | V    |

|                          |                                                        | PSTOP = H,VBAT=3.6V                                                       |        |        | 3                                          | V    |

|                          |                                                        | PSTOP = L<br>VBUS = 5V, VCC = 4.5V                                        | 17     | 25     | 30                                         | mA   |

| $I_{VCC\_LIM}$           | VCC current limit                                      | PSTOP = L<br>VBUS = 9V, VCC = 4.5V                                        |        | 160    |                                            | mA   |

|                          |                                                        | PSTOP = H                                                                 |        |        | 1                                          | mA   |

| V                        | VDRV regulation voltage                                | change pump connected<br>VBUS = 5V, IDRV = 0mA                            | 5.8    | 6.2    | 6.5                                        | V    |

| $V_{DRV}$                | VDIXV legulation voltage                               | change pump connected<br>VBUS = 9V, IDRV = 30mA                           | 5.7    | 6.1    | 6.4                                        | V    |

| R <sub>HS/LS_PU</sub>    | High/low side MOS driver pull up resistor              |                                                                           |        | 4      |                                            | Ω    |

| R <sub>HS/LS_PD</sub>    | High/low side MOS driver pull down resistor            |                                                                           |        | 1      |                                            | Ω    |

| REFERENC                 | E VOLTAGE IN CHARGING MODE                             |                                                                           |        |        |                                            |      |

| V <sub>BATS_ext</sub>    | VBATS reference voltage for external setting           | VBAT_SEL = 1                                                              | 1.197  | 1.203  | 1.209                                      | V    |

| $V_{\text{BATS\_int}}$   | VBATS accuracy for internal setting, over VBATS target | VBAT_SEL = 0, CSEL = 00<br>VCELL_SET=000~111                              | -0.5   |        | 0.5                                        | %    |

| V <sub>TRICKLE_int</sub> | Trickle charge threshold voltage for internal setting  | VBAT_SEL = 0, Cell number = N<br>VCELL_SET = 000~1111,<br>TRICKLE_SET = 0 | 2.73*N | 2.94*N | 3.15*N                                     | V    |

|                          |                                                        | VBAT_SEL = 0, Cell number = N                                             | 2.31*N | 2.52*N | 3<br>30<br>1<br>6.5<br>6.4<br>1.209<br>0.5 | V    |

|                              |                                              | VCELL_SET = 000~1111,<br>TRICKLE_SET = 1                         |        |        |       |               |

|------------------------------|----------------------------------------------|------------------------------------------------------------------|--------|--------|-------|---------------|

| V                            | Trickle charge threshold for                 | VBAT_SEL = 1,<br>TRICKLE_SET = 0                                 | 65     | 70     | 75    | %             |

| $V_{TRICKLE\_ext}$           | external setting, over VBAT target           | VBAT_SEL = 1,<br>TRICKLE_SET = 1                                 | 55     | 60     | 65    | %             |

| V <sub>EOC</sub>             | EOC voltage threshold, over VBAT target      | VBAT_SEL = 0/1                                                   | 97%    | 98%    | 99%   |               |

| $V_{RECH}$                   | Recharge threshold voltage, over VBAT target | VBAT_SEL = 0/1                                                   | 94.8%  | 95.8%  | 96.8% | $\rangle_{/}$ |

|                              |                                              | 4.5V target VINREG_SET = 0x2C, VINREG_RATIO = 0                  | 4.3    | 4.5    | 4.7   | ٧             |

| Vinreg                       | VINDEC reference veltage                     | 15V target VINREG_SET = 0x95, VINREG_RATIO = 0                   | 14.7   | 15     | 15.3  | ٧             |

|                              | VINREG reference voltage                     | 4.48V target VINREG_SET = 0x6F, VINREG_RATIO = 1                 | 4.4    | 4.5    | 4.6   | V             |

|                              |                                              | 10V target VINREG_SET = 0xF9, VINREG_RATIO = 1                   | 9.8    | 10     | 10.2  | ٧             |

| $V_{BAT\_OVP}$               | VBAT OVP threshold, over VBAT target         | VBAT_SEL = 0/1                                                   | 103%   | 105.5% | 108%  |               |

| V <sub>CLAMP</sub>           |                                              |                                                                  |        | 125    |       | mV            |

| REFERENC                     | E VOLTAGE IN DISCHARGING MOD                 | E C                                                              |        |        |       |               |

| V <sub>FB</sub>              | FB reference voltage for external setting    | FB_SEL = 1, VBUSREF_E_REF target from 0.5V to 2.048V             | -2%    |        | 2%    |               |

| $V_{\scriptscriptstyle BUS}$ | VBUS reference voltage accuracy              | FB_SEL = 0<br>VBUS_RATIO = 1 (5x)<br>VBUS = 3.6 ~10.24V          | -2%    |        | 2%    |               |

| V BUS                        | for internal setting                         | FB_SEL = 0<br>VBUS_RATIO = 0 (12.5x)<br>VBUS = 9 ~ 24V           | -2%    |        | 2%    |               |

| V                            | VBUS OVP threshold, rising edge              | VBUSREF_I_SET = 1V<br>VBUSREF_E_SET = 1V                         | 107.3% | 110%   | 113%  |               |

| V <sub>BUS_OVP</sub>         | Hysteres is                                  | VBUSREF_I_SET = 1V<br>VBUSREF_E_SET = 1V                         |        | 3%     |       |               |

| CURRENT I                    | LIMIT                                        |                                                                  |        |        |       |               |

|                              | $\sim$                                       | Charging mode, 6A target IBUS_RATIO = 01 (6x) IBUS_LIM = 0x7F    | -10%   |        | 10%   |               |

| 5                            | IDLIC augment limit                          | Charging mode, 3A target IBUS_RATIO = 10 (3x) IBUS_LIM = 0x7F    | -10%   |        | 10%   |               |

| IBUS_LIM                     | IBUS current limit accuracy                  | Discharging mode, 6A target IBUS_RATIO = 01 (6x) IBUS_LIM = 0x7F | -10%   |        | 10%   |               |

|                              |                                              | Discharging mode, 3A target IBUS_RATIO = 10 (3x) IBUS_LIM = 0x7F | -10%   |        | 10%   |               |

|                        |                                                                                                                                                                                                                                                                                                                                                | Charging mode, 6A target IBAT_RATIO = 0 (6x) IBAT_LIM = 0xFF      | -10% |       | 10%  |     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|-------|------|-----|

|                        | IDAT                                                                                                                                                                                                                                                                                                                                           | Charging mode, 12A target IBAT_RATIO = 1 (12x) IBAT_LIM = 0xFF    | -10% |       | 10%  |     |

| I <sub>BAT_LIM</sub>   | IBAT current limit accuracy                                                                                                                                                                                                                                                                                                                    | Discharging mode, 6A target IBAT_RATIO = 0 (6x) IBAT_LIM = 0xFF   | -15% |       | 15%  |     |

|                        | Trickle charge current, over IBUS_LIM setting  EOC current threshold, over IBUS_LIM / IBAT_LIM setting  RROR AMPLIFIER  DIT Error amplifier gm  Error amplifier output resistance  COMP sink current  COMP source current  FB pin input bias current  VITCHING  Switching frequency  DWER PATH MANAGEMENT  U_PGATE  PGATE pin pull up resistor | Discharging mode, 12A target IBAT_RATIO = 1 (12x) IBAT_LIM = 0xFF | -15% | ./    | 15%  |     |

| <b>I</b>               |                                                                                                                                                                                                                                                                                                                                                |                                                                   |      | 10%   |      |     |

| ITRICKLE               |                                                                                                                                                                                                                                                                                                                                                |                                                                   |      | 22%   |      |     |

|                        |                                                                                                                                                                                                                                                                                                                                                | EOC_SET= 0                                                        |      | 10%   |      |     |

| I <sub>EOC</sub>       | IBUS_LIM / IBAT_LIM setting                                                                                                                                                                                                                                                                                                                    | EOC_SET= 1                                                        |      | 4%    |      |     |

| ERROR AM               | IPLIFIER                                                                                                                                                                                                                                                                                                                                       |                                                                   | V    |       |      |     |

| $Gm_EA$                | Error amplifier gm                                                                                                                                                                                                                                                                                                                             |                                                                   | 0.12 | 0.15  | 0.18 | mS  |

| R <sub>OUT</sub>       | Error amplifier output resistance (1)                                                                                                                                                                                                                                                                                                          |                                                                   |      | 20    |      | МΩ  |

| I <sub>SINK_COMP</sub> | COMP sink current                                                                                                                                                                                                                                                                                                                              | LOOP_SET = 0/1                                                    |      | 25    |      | μΑ  |

| 1                      | COMP course current                                                                                                                                                                                                                                                                                                                            | LOOP_SET = 0                                                      |      | 18    |      | μA  |

| 'SRC_COMP              | COMP source current                                                                                                                                                                                                                                                                                                                            | LOOP_SET = 1                                                      |      | 32    |      | μΑ  |

| I <sub>BIAS_FB</sub>   | FB pin input bias current                                                                                                                                                                                                                                                                                                                      | FB_SEL = 1 FB in regulation                                       |      |       | 50   | nA  |

| SWITCHING              | G                                                                                                                                                                                                                                                                                                                                              |                                                                   |      |       |      |     |

|                        |                                                                                                                                                                                                                                                                                                                                                | FREQ_SET = 00 (150kHz)                                            | 140  | 155   | 170  | kHz |

| $f_{\text{SW}}$        | Switching frequency                                                                                                                                                                                                                                                                                                                            | FREQ_SET = 01 (300kHz)                                            | 270  | 305   | 330  | kHz |

|                        |                                                                                                                                                                                                                                                                                                                                                | FREQ_SET = 11 (450kHz)                                            | 400  | 450   | 500  | kHz |

| POWER PA               | TH MANAGEMENT                                                                                                                                                                                                                                                                                                                                  |                                                                   |      |       |      |     |

| R <sub>PU_PGATE</sub>  | PGATE pin pull up resistor                                                                                                                                                                                                                                                                                                                     | EN_PGATE = 0                                                      |      | 20    |      | kΩ  |

| R <sub>PD_PGATE</sub>  | PGATE pin pull down resistor                                                                                                                                                                                                                                                                                                                   | EN_PGATE = 1                                                      |      | 6     |      | kΩ  |

| $V_{\text{CLAMP}}$     | Clamp voltage from VBUS to PGATE pin                                                                                                                                                                                                                                                                                                           | EN_PGATE = 1                                                      | 6.9  | 7.35  | 7.7  | V   |

| $R_{RD\_GPO}$          | GPO pin pull down resistor                                                                                                                                                                                                                                                                                                                     | GPO_CTRL = 1                                                      |      | 6     |      | kΩ  |

| DETECTION              | V                                                                                                                                                                                                                                                                                                                                              |                                                                   |      |       |      |     |

| V <sub>AC_DET</sub>    | AC detection threshold                                                                                                                                                                                                                                                                                                                         |                                                                   | 2.9  | 3.1   | 3.4  | V   |

| VSHORT                 | Short circuit detection threshold                                                                                                                                                                                                                                                                                                              |                                                                   | 0.95 | 1     | 1.05 | V   |

| I2C AND LC             | OGIC CONTROL                                                                                                                                                                                                                                                                                                                                   |                                                                   |      |       |      |     |

| R <sub>PD</sub>        | PSTOP pin internal pull down resistor                                                                                                                                                                                                                                                                                                          |                                                                   | 0.75 | 1     | 1.25 | ΜΩ  |

| V <sub>IL</sub>        | PSTOP, SCL, SDA input low voltage                                                                                                                                                                                                                                                                                                              |                                                                   |      |       | 0.4  | V   |

| V <sub>IH</sub>        | PSTOP, SCL, SDA input high voltage                                                                                                                                                                                                                                                                                                             |                                                                   | 1.2  |       |      | V   |

| I <sub>SINK_INT</sub>  | INT pin sink current                                                                                                                                                                                                                                                                                                                           | V <sub>INT</sub> = 0.4V                                           | 0.3  | 0.375 | 0.45 | mA  |

| I <sub>SINK_SCL/SDA</sub> | SCL/SDA pin sink current          | V <sub>SCL/SDA</sub> = 0.4V                                              |     | 100 |     | mA |

|---------------------------|-----------------------------------|--------------------------------------------------------------------------|-----|-----|-----|----|

| t <sub>PULSE</sub>        | Interrupt pulse width (logic low) |                                                                          | 0.6 | 1   | 1.5 | ms |

| SOFTSTART                 | Г                                 |                                                                          |     |     |     |    |

| t <sub>deglitch</sub>     | Deglitch time for charging        | PSTOP = L, OTG_SET = 0 VBUS = 5V, from PSTOP low to IC starting charging |     | 220 |     | ms |

| t <sub>ss</sub>           | Internal soft-start time          | VBUS from 0V to 5V in discharging mode VBUS_Ratio = 1 (5x)               |     | 12  | 1   | ms |

| THERMAL S                 | SHUTDOWN                          |                                                                          |     |     | V   |    |

| T <sub>SD</sub>           | Thermal shutdown temperature (1)  |                                                                          |     | 165 |     | °C |

|                           | Thermal shutdown hysteresis (1)   |                                                                          |     | 15  |     | °C |

## 8 Detailed Description

## 8.1 Charging Mode

Charging mode and discharging mode is selected by EN\_OTG bit.

When EN\_OTG bit is 0, the IC works in charging mode. The current flows from VBUS to VBAT to charge the battery cells.

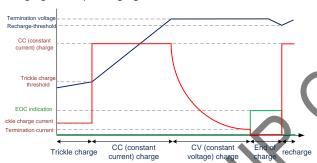

When in charging mode, the IC charges the battery cells according to below typical charging profile. When battery voltage is lower than trickle charge threshold, the IC charges the cells with small charging current; when cell voltage is higher than the threshold, the IC enters into Constant Current charging phase, and charges the cells with constant current set by IBUS limit or IBAT limit. When the cell voltage reaches the termination voltage target, the IC enters into Constant Voltage charge phase, and charges the cells with gradually decreased current until the current is lower than termination current threshold. Once termination voltage and termination current conditions are satisfied, the IC enters into End of Charge phase. In this phase the IC can either terminate the charging or keep charging the cells.

Figure 1 Typical Charging Profile

#### 8.1.1 Trickle Charge

The trickle charge voltage threshold can be set to 60% or 70% of 4.2V/cell by TRICKLE\_SET bit. When in trickle charge phase, the charging current is reduced to a small value for the good of battery cells. If ICHAR\_SEL bit is 0, the IBUS is reduced to 1/10 of the IBUS current limit set value; if ICHAR\_SEL bit is 1, the IBAT is reduced to 1/10 of IBAT current limit set value.

If trickle charging phase is not needed, the user can set DIS\_TRICKLE bit to 1 to disable it.

## 8.1.2 CC Charge (Constant Current Charge)

When cell voltage is higher than the trickle threshold, the IC charges the battery cells with constant current set by IBUS limit or IBAT limit, which are set respectively through IBUS\_LIM\_SET and IBAT\_LIM\_SET registers. The current limit value can be changed dynamically, and is also related to the current sense resistor and ratio bits. Please see Register Map section for details.

In charging mode, the IC regulates the current which reaches

its current limit value first. For example, if IBUS current limit is set to 3A, IBAT limit is set to 10A, and when IBUS reaches 3A, IBAT is only 6A, which is much lower than IBAT limit 10A, then the IC limits the IBUS at 3A.

It is not allowed to set any of the current limits to 0A. Keep the minimum current limit above 0.3A.

#### 8.1.3 CV Charge (Constant Voltage Charge)

The battery target voltage can be set internally, by CSEL bits and VCELL\_SET bits. The CSEL bits set the battery cell numbers connected in series, and VCELL\_SET bits set the battery voltage per cell. For example, if the battery cells are in xp2s connection (several cells are connected in parallel, and two cells in series) and the cell voltage is 4.3V, the user should set CSEL to 01 (2S), and set VCELL\_SET bits to 011 (4.3V).

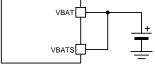

When the battery charging voltage is set internally, the user should connect VBATS pin to VBAT terminal to sense the battery voltage, and the VBAT\_SEL bit should be set to 0.

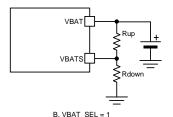

If VBAT\_SEL is set to 1, it means the battery voltage is set externally. Under this condition, the user should use resistor divider at VBATS pin to set the target voltage as below. VCELL\_SET and CSEL bits don't work. The reference of VBATS is 1.2V.

$$VBAT = V_{BATS\_REF} \times \left(1 + \frac{R_{UP}}{R_{DOWN}}\right)$$

A. VBAT\_SEL = 0

Figure 2 Battery voltage setting

When the battery cell voltage reaches 98% of the cell target voltage, the IC enters into CV charge phase. In this phase, the VBAT voltage is regulated at target value, and the charging current reduces gradually.

#### 8.1.4 EOC (End of Charge)

When both of below voltage condition and current condition for EOC detection are satisfied, the IC enters into EOC

phase, and informs the MCU through EOC interrupt bit.

- 1. the cell voltage is higher than 98% of set value

- the IBUS or IBAT current (decided by ICHAR\_SEL bit) is lower than 1/10 or 1/25 (decided by EOC\_SET bit) of its current limit value

In EOC phase, the IC can terminate the charging process or keep charging the battery cells, which can be set by DIS\_TERM bit. If IC keeps charging, it regulates the battery cell voltage at set value.

#### 8.1.5 Recharge

If the IC terminates the charging process after EOC is detected, the battery voltage may drop slowly due to leakage or operation current from battery cells. Once the VBAT voltage drops below 95% of the set voltage, the EOC bit is cleared, and the IC enters into CC charge phase and recharges the battery.

#### 8.1.6 Self-adaptive Charging Current (VINREG)

The IC features dynamic power management. The allowed minimum VBUS operation voltage is VINREG threshold, which can be set by VINREG\_SET register and VINREG\_RATIO bit dynamically. During charging, if the IBUS charging current is higher than adapter's current capability, the adapter will be overloaded and the VBUS voltage is pulled low. Once the IC detects the VBUS voltage drops at VINREG threshold, it reduces the charging current automatically and regulates the VBUS voltage at VINREG threshold.

#### 8.1.7 Battery Impedance Compensation

The IC provides the function of battery impedance compensation. User can set the impedance through IRCOMP bits, then the VBAT target voltage in CV phase is compensated as

$VBAT\_cmp = VBAT\_set + min(IBAT \cdot IRCOMP, VCLAMP)$

Where,

VBAT\_cmp is the compensated battery voltage target; VBAT\_set is the originally set battery termination target; IBAT is the charging current at battery side; IRCOMP is the resistance compensation value set by IRCOMP bits; VCLAMP is the allowed maximum compensation value, fixed at 125mV.

User should carefully evaluate the real battery impedance. If the value set by IRCOMP bits is higher than the real value, it will cause over charge.

#### 8.2 Discharging Mode

When EN\_OTG bit is set to1, the IC enters into discharging mode. In discharging mode, the battery (VBAT) is discharged and the current flows from VBAT to VBUS.

If FB\_SEL is set to 0, the VBUS output voltage is set internally, through VBUSREF\_I\_SET and VBUSREF\_I\_SET2 registers and the VBUS\_RATIO bit. The VBUS can be

changed dynamically, and the recommended VBUS voltage range is from 3V to 36V. When VBUS is lower than 10.24V, it is suggested to set the VBUS\_RATIO to 5x, and so the minimum changing step is 10mV/step; when VBUS is higher than 10.24V, VBUS\_RATIO should be set to 12.5x, and the minimum changing step is 25mV/step.

If FB\_SEL is set to 1, the VBUS voltage target is set externally, that is, by the resistor divider connected at FB pin, and can be calculated as below.

Even if VBUS is set externally, the user can still change the VBUS voltage dynamically by changing the reference voltage VBUSREF\_E through VBUSREF\_E\_SET and VBUSREF\_E\_SET2 registers. The default VBUSREF\_E is 1V, and recommended VBUSREF\_E voltage range is from 0.7V to 2.048V.

Please see Register Map section for details.

The IBUS current limit and IBAT current limit are still functional in discharging mode and can be changed dynamically.

It is not allowed to set any of the current limits to 0A. Keep the minimum current limit above 0.3A.

#### 8.2.1 Soft Start

The IC integrates soft-start control to generate VBUS voltage in discharging mode. When VBUS is lower than V<sub>SHORT</sub> (typ. 1V), both IBUS and IBAT current limits are fold back to 1/10 of the setting value. Meanwhile, the IC ramps up the internal reference voltage gradually (~10ms) to avoid inrush current.

If there is a load at VBUS at the beginning of the startup, the IC may fail to boost the VBUS voltage beyond V<sub>SHORT</sub> due to the 1/10 current limits for both IBUS and IBAT. If startup with loading is required, user shall set the DIS\_ShortFoldBack bit to 1 to disable the current limit fold back function. After startup, the user can set DIS\_ShortFoldBack bit back to 0, so to enable this function for short circuit protection. See VBUS Short Protection section for details.

#### 8.2.2 Slew Rate Setting

When the VBUS voltage is changed dynamically through reference voltage (VBUSREF\_I\_SET and VBUSREF\_I\_SET2 registers or VBUSREF\_E\_SET and VBUSREF\_E\_SET2 registers), the reference voltage change rate can be controlled through SLEW\_SET bits. For example, the VBUS is set in internal way with 5x ratio, and the VBUSREF\_I = 1V at first (VBUS = 5V), then the user sets the VBUSREF\_I voltage to 1.6V to get 8V output. If the slew rate is 2mV/ µs, the VBUS voltage will increase to 8V in 600mV / 2mV/µs = 300µs.

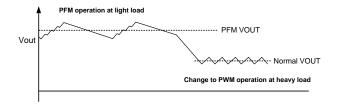

#### 8.2.3 PFM Operation

The IC supports PFM operation in discharging mode by setting EN\_PFM bit to 1. In PWM mode, the IC always works with constant switching frequency for the whole load range. This helps achieve the best output voltage performance, but

the efficiency is low at light load condition because of the high switching loss.

In PFM mode, the IC still works with constant switching frequency under heavy load condition, but under light load condition, the IC automatically changes to pulse frequency modulation operation to reduce the switching loss. The efficiency can be improved under light load condition while output voltage ripple will be a little larger compared with PWM operation. Below figure shows the output voltage behavior of PFM mode.

Figure 3 PFM mode illustration

#### 8.3 ADC for Voltage and Current Monitor

The IC integrates a 10-bit ADC, so the IC can monitor the VBUS/VBAT voltages and IBUS/IBAT current no matter in charging mode or discharging mode. Besides these, the IC provides an analog input: ADIN pin for 10-bit ADC sampling. The maximum voltage the ADC can sample at ADIN pin is 2.048V, and the sampling resolution is 2mV/step. The ADC function is enabled after AD\_START bit is set to 1. When ADC is enabled in standby mode, the IC will 0.5mA~1mA operation current. Please see Register Map section for details.

#### 8.4 Power Path Management

The IC offers power path management function at PGATE and GPO pins. The PGATE pin can be used to drive PMOS connected at VBUS. The PGATE pin is connected to a 6 k $\Omega$  pull down resistor internally when EN\_PGATE is set to 1, and the maximum voltage between VBUS and PGATE is clamped at 7.35V; when EN\_PGATE is set to 0, PGATE pin is connected to VBUS rail through a 20 k $\Omega$  pull up resistor internally

The GPO pin is an open drain output, so external pull up resistor is needed. When GPO\_CTRL bit is set to 0, GPO outputs high impedance; when GPO\_CTRL is set to1, GPO is pulled down internally and the pull down resistance is 6 k $\!\Omega$ .

User can use PGATE pin and GPO pin to control the isolation MOSFETs between adapter input and USB output as shown in Typical Application Circuit. However, the MCU or system controller controls the bits through I2C interface, which takes time for communication, so the PMOS may not be turned on/off very quickly. In the application where the isolation PMOS needs to be controlled very fast, it is suggested to use the I/O pins of MCU to control the PMOS on/off directly.

#### 8.5 Phone Insert Detection

If connecting INDET pin to USB-A port as shown in Typical Application Circuit, the IC can detect the phone detection. Once the IC detects a phone is inserted, it sets the INDET interrupt bit to inform MCU. The INDET bit is cleared after it is read by MCU.

# 8.6 Adapter Attachment / Detachment Detection

If connecting ACIN pin to Micro-USB port as shown in Typical Application Circuit, the IC can detect the attachment / detachment of the adapter.

Once the ACIN pin voltage is higher than 3V, which means the adapter is inserted, the IC sets the AC\_OK interrupt bit to inform MCU about the attachment. If the ACIN pin voltage is lower than 3V, which means the adapter is removed, the IC clears AC\_OK bit to inform the MCU about the detachment.

## 8.7 Switching and Frequency Dithering

The IC switches in fixed frequency which can be adjusted through FREQ\_SET bits. The switching dead time can also be set through DT\_SET pins. Please see Register Map section for details.

The IC also offers frequency dithering function. This function can be enabled by setting EN\_DITHER bit to 1. When the function is enabled, the switching frequency is not fixed, but varies within +/- 5% range. For example, if the switching frequency is set to 300kHz (FREQ\_SET = 01), the frequency will change from 285kHz to 315kHz gradually and then back to 285kHz back and forth. The time it varies from the lowest to the highest frequency or from highest to lowest frequency can be controlled by a capacitor connected at PGATE/DITHER pin as below equation shows. For example, if 100nF capacitor is connected, the time is 1.2 ms.

$$T_{dither} = \frac{120 \text{ mV} \times \text{C}}{10 \mu \text{A}}$$

When EN\_DITHER is set to 1, the PGATE driver function is disabled, and the PGATE/DITHER pin only operates for dithering function.

#### 8.8 VCC Regulator and Driver Supply

The IC integrates a regulator which is powered by VBUS voltage and generates a 5V voltage at VCC pin with typically 25 mA driving capability.

When in Standby mode, the VCC voltage is not regulated and has very limited current capability. It is not suggested to use VCC in Standby mode.

The internal driving circuit is powered from VDRV pin, and user should provide a supply at VDRV pin to power the circuit. The user can connect VCC to VDRV directly, or connect an external power supply to VDRV. Besides the two ways, the IC offers a charge pump driver at CP pin, which can pump the VCC voltage to power VDRV pin. With charge pump circuit, the IC can regulate the VDRV voltage at 6V.

A. connect VC to VDRV directly

B. Use charge pump to power VDRV

B. Use external power supply

## Figure 4 Supply for VDRV

## 8.9 Standby Mode

When /CE signal is low and PSTOP signal is high, the IC enters into Standby mode. In this mode, the IC stops switching to save the quiescent current. The other functions are still valid, and the MCU can still control the IC through I2C. However, if ADC function is enabled in Standby mode, the quiescent current will be increased to 0.5mA~1mA.

#### 8.10 Shutdown Mode

When CE signal is high, the IC enters into Shutdown mode. In this mode, the IC stops working and disables the I2C interface to save the power. When /CE signal is pulled low, the IC goes into Standby mode or Active mode. /CE signal is pulled down by internal resistor.

#### 8.11 Protection

#### 8.11.1 VBUS Over Voltage Protection

User can enabled / disable VBUS over voltage protection in discharging mode by DIS\_OVP bit. When OVP is enabled, the IC stops switching when VBUS is higher than the target voltage by 10%.

#### 8.11.2 VBAT Over Voltage Protection

The IC implements VBAT over voltage protection in both charging mode and discharging mode. Once the VBAT voltage is higher than target voltage by 10%, the IC stops switching.

#### 8.11.3 VBUS Short Protection

In discharging mode, if the VBUS voltage is detected lower than  $V_{SHORT}$  (typ. 1V), the IC sets the VBUS\_SHORT interrupt bit to inform the MCU. In the same time, it reduces IBUS limits to 10% of the set values and IBAT limit to 22% of the set value at the same time to protect the IC. If DIS\_ShortFoldBack bit is set to 1, the current limits will not be reduced

#### 8.11.4 Over Temperature Protection

When the IC detects the junction temperature is higher than 165°C, the IC stops switching to protect the chip, and sets the OTP interrupt bit to inform the MCU. It resumes switching once the temperature drops below 15°C.

#### 8.12 I2C and Interrupt

#### 8.12.1 I2C Interface

The IC features I2C interface, so the MCU or controller can control the IC flexibly. The 7-bit I2C address of the chip is 0x74 (8-bit address is 0xE8 for write command, 0xE9 for read command). The SDA and SCL pins are open drain and must be connected to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. The I2C interface supports both standard mode (up to 100kbits) and fast mode (up to 400k bits with 5 k $\Omega$  pull up resistor at SCL pin and SDA pin respectively).

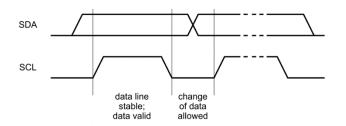

#### 8.12.1.1 Data Validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

Figure 5 Bit transfer on the I2C bus

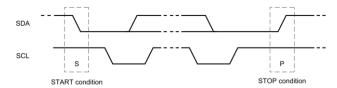

#### 8.12.1.2 START and STOP Conditions

All transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after the STOP condition.

Figure 6 START and STOP conditions

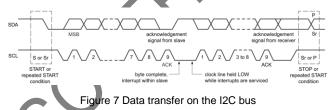

#### 8.12.1.3 Byte Format

Every byte put on the SDA line must be eight bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit. Data is transferred with the Most Significant Bit (MSB) first. If a slave cannot receive or transmit another complete byte of data until it has performed some other function, for example servicing an internal interrupt, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

8.12.1.4 Acknowledge (ACK) and Not Acknowledge (NACK)

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. During data is transferred, the master can either be the transmitter or the receiver. No matter what it is, the master generates all clock pulses, including the acknowledge ninth clock pulse.

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse.

When SDA remains HIGH during this ninth clock pulse, this is defined as the Not Acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

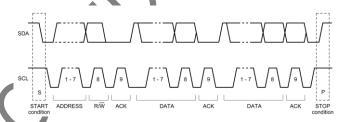

#### 8.12.1.5 The slave address and R/W bit

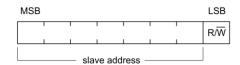

Data transfers follow the format shown in below. After the START condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W) — a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition.

Figure 8 A complete data transfer

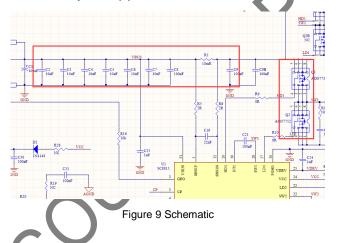

Figure 9 The first byte after the START procedure

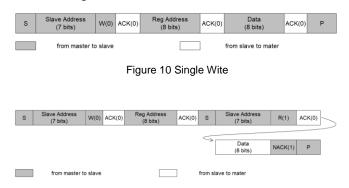

#### 8.12.1.6 Single Read and Write

Figure 11 Single Read

If the register address is not defined, the charger IC send back NACK and go back to the idle state.

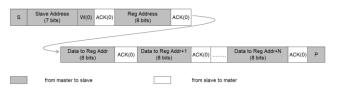

#### 8.12.1.7 Multi-Read and Multi-Write

The IC supports multi-read and multi-write for continuous registers.

Figure 12 Multi-Write

Figure 13 Multi-Read

#### 8.12.2 Interrupt

When AC\_OK/VBUS\_SHORT/OTP/EOC is set to 1, or clear to 0, the IC sends an interrupt pulse as below at INT pin to inform MCU. But when INDET only is set to 1, the IC sends an interrupt pulse. It is summarized as below:

| Status Signal | Interrupt Triggering Mechanism |  |

|---------------|--------------------------------|--|

| Reserved      |                                |  |

| AC_OK      | Rising edge or falling edge triggers 1ms_pulse INT |

|------------|----------------------------------------------------|

| INDET2     | Only rising edge triggers 1ms_pulse INT            |

| INDET1     | Only rising edge triggers 1ms_pulse INT            |

| VBUS_SHORT | Logic high triggers continuous INT                 |

| ОТР        | Rising edge or falling edge triggers 1ms_pulse INT |

| EOC        | Rising edge or falling edge triggers 1ms_pulse INT |

| Reserved   |                                                    |

The interrupt pulse at INT pin is as follow:

Figure 14 Interrupt pulse at INT pin

The INDET bit is read and clear type. Except INDET, all other bits in Status register represent the real time status. User can mask the interrupt output of any bit by setting its corresponding bit in Mask register. When the mask bit is set, the corresponding status bit is still set, but the IC doesn't send the interrupt at INT pin.

## 9 Application Information

#### 9.1 Capacitor Selection

The switching frequency of the IC is in the range of 150kHz ~ 450kHz. Since MLCC ceramic capacitor has good high frequency filtering with low ESR, above 60µF X5R or X7R capacitors with higher voltage rating then operating voltage with margin is recommended. For example, if the highest operating Vin/Vout voltage is 12V, select at least 16V capacitor and to secure enough margin, 25V voltage rating capacitor is recommended.

The high capacitance polymer capacitor or tantalum capacitor can be used for input and output but capacitor voltage rating must be higher than the highest operating voltage with enough margin. The high frequency characteristics of these capacitors are not as good as ceramic capacitor, so at least 10µF ceramic capacitor should be placed in parallel to reduce high frequency ripple.

#### 9.2 Inductor Selection

2.2 µH to 4.7 µH inductor is recommended for loop stability. The peak inductor current in discharging mode can be calculated as

$$\begin{split} &\text{IL\_peak} = \text{IBAT} + \frac{\text{VBAT} \cdot (\text{VBUS-VBAT} \cdot \eta \ )}{2 \cdot \text{fsw} \cdot \text{L} \cdot \text{VBUS}} \quad (\text{VBUS} {\ge} \text{VBAT}) \\ &\text{IL\_peak} = \text{IBUS} + \frac{\text{VBUS} \cdot (\text{VBAT - VBUS})}{2 \cdot \text{fsw} \cdot \text{L} \cdot \text{VBAT} \cdot \eta} \quad (\text{VBUS} {<} \text{VBAT}) \end{split}$$

where IBAT is the battery current at VBAT side, and can be calculated as

$$IBAT = \frac{VBUS \cdot IBUS}{\eta \cdot VBAT}$$

$\eta$  is the power conversion efficiency. User can use 90% for calculation.

fsw is the switching frequency

L is the inductor value

The peak inductor current in charging mode can be calculated as

$$\begin{split} &\text{IL\_peak} = \text{IBAT} + \frac{\text{VBAT} \cdot (\text{VBUS-VBAT})}{2 \cdot \text{fsw} \cdot \text{L} \cdot \text{VBUS} \cdot \eta} \; (\text{VBUS>VBAT}) \\ &\text{IL\_peak} = \text{IBUS} + \frac{\text{VBUS} \cdot (\text{VBAT-VBUS} \cdot \eta)}{2 \cdot \text{fsw} \cdot \text{L} \cdot \text{VBAT}} \; (\text{VBUS} \leq \text{VBAT}) \end{split}$$

where IBAT is the battery charging current at VBAT side, and can be calculated as

$$IBAT = \frac{VBUS \cdot IBUS \cdot \eta}{VBAT}$$

$\eta$  is the power conversion efficiency. User can use 90% for calculation.

fsw is the switching frequency

L is the inductor value

When selecting inductor, the inductor saturation current must be higher than the peak inductor current with enough margin (20% margin is recommended). The rating current of the inductor must be higher than the battery current.

The inductor DC resistance value (DCR) affects the conduction loss of switching regulator, so low DCR inductor is recommended especially for high power application. The conductor loss of inductor can be calculated roughly as

$$PL DC = IL^2 DCR$$

IL is the average value of inductor current, and it equals to IBAT or IBUS.

Besides DC power loss, there are also inductor AC winding loss and inductor core loss, which are related to inductor peak current. Normally, higher peak current causes higher AC loss and core loss. The user can consult with the inductor vendor to select the inductors which have small ESR at high frequency and small core loss.

#### 9.3 Current Sense Resistor

The RSNS1 and RSNS2 are current sense resistors. 10 m $\Omega$  should be used for RSNS1 to sense IBUS current, 5 m $\Omega$  or 10 m $\Omega$  used for RSNS2 to sense IBAT current (10 m $\Omega$  supports higher battery current limit accuracy, and 5 m $\Omega$  supports higher efficiency). Resistor of 1% or higher accuracy and low temperature coefficient is recommended.

Note: If the user wants to use other resistor values, please contact factory for support.

The resistor power rating and temperature coefficient should be considered. The power dissipation is roughly calculated as  $P=I^2R$ , and I is the highest current flowing through the resistor. The resistor power rating should be higher than the calculated value.

Normally the resistor value is varied if the temperature increased and the variation is decided by temperature coefficient. If high accuracy of current limit is required, select lower temperature coefficient resistor as much as possible.

#### 9.4 MOSFET Selection

The IC integrates two power MOSFETs, and the user should add two external power MOSFETs at VBAT side.

The  $V_{DS}$  of MOSFET should be higher than the highest operating voltage with enough margin (recommend more than 10V higher). For example, if the highest operating voltage is 20V, at least 30V rated  $V_{DS}$  MOSFET should be selected; If the highest operating voltage is 24V, 40V  $V_{DS}$  voltage rating should be selected.

The  $V_{GS}$  voltage rating of MOSFET should be selected higher than 8V. Considering PCB parasitic parameters during operation, MOSFET  $V_{GS}$  voltage might be higher than  $V_{DRV}$

voltage due to transient overshoot, so  $10V\ V_{GS}$  is recommended to secure sufficient margin.

The MOSFET current  $I_D$  should be higher than the highest battery current with enough margin.

To ensure the sufficient current capability in relatively high temperature circumstance, the current rate at T<sub>A</sub>=70°C or T<sub>C</sub>

=  $100^{\circ}$ C should be considered. In addition, the power dissipation value  $P_D$  should also be considered and higher  $P_D$  is better in applications. Make sure that MOSFET power consumption must not exceed  $P_D$  value.

The MOSFET  $R_{DS(ON)}$  and input capacitor  $C_{ISS}$  impact power efficiency directly. Typically, lower  $R_{DS(ON)}$  MOSFET has higher  $C_{ISS}$ . The  $R_{DS(ON)}$  is related to conduction loss. Higher  $R_{DSON}$  results in higher conduction loss, thus lower efficiency and higher thermal dissipation; the  $C_{ISS}$  is related to MOSFET switch on/off time, and longer on/off time results in higher switching loss and lower efficiency. The proper MOSEFT should be selected based on tradeoff between the  $R_{DS(ON)}$  and  $C_{ISS}$ .

If high  $C_{\rm ISS}$  MOSFET is selected, the switching on and off time become longer, then the dead time should be adjusted to avoid simultaneous turn on for both high side and low side MOSFETs.

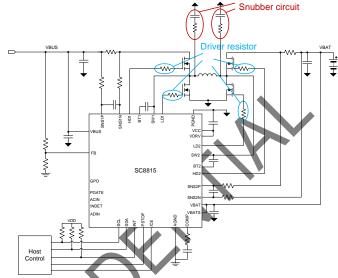

#### 9.5 Driver Resistor and SW Snubber Circuit

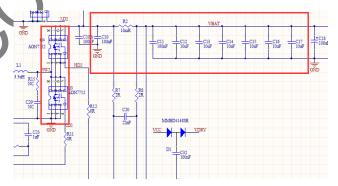

To adjust MOSFET switching time and switching overshoot for EMI debugging, it is recommended to add series resistor (0603 size) for gate driving signal (HD1 to MOS gate, LD1 to MOS gate, LD2 to MOS gate, and HD2 to MOS gate), and RC snubber (0603 size) circuit at SWx, as shown below.

The driver resistor should be placed near MOS. At first, use  $0\Omega$  resistors; if switching overshoot is big, increase the resistor value to slow down the switching speed. It is suggested to keep the resistor value <  $10~\Omega$ . While the switching speed gets slower, the default dead time may not be enough to avoid overshoot of the power MOSFETs. So if higher than  $10\Omega$  is needed, user should increase the dead time if necessary.

The RC snubber circuit at SWx node is also helpful in absorbing the high frequency spike at SWx node, so to improve EMC performance. User can leave RC components as NC at the beginning, and adjust the value to improve the EMC performance if necessary. Normally user can try  $2.2\Omega$  and 1nF for the snubber. If EMC should be improved further, reduce the resistor value (like 1  $\Omega$  or even lower) and increase the capacitor value (like 2.2nF or even higher).

Figure 15 Driver resistor and snubber circuit

## 9.6 Layout Guide

- 1. The 1uF capacitors connected at VBUS/VBAT/VCC/VDRV pins should be placed near the IC, and their ground connection to the ground pins should be as short as possible.

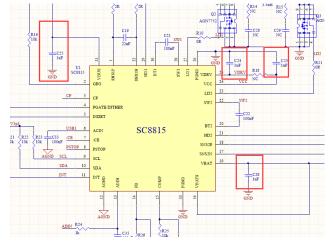

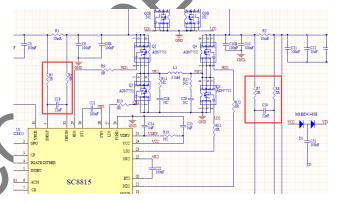

- a. component(s) on schematic:

Figure 16 Schematic

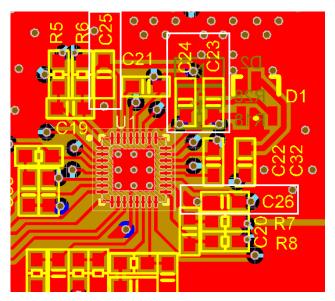

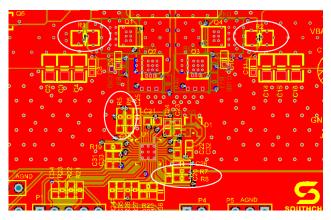

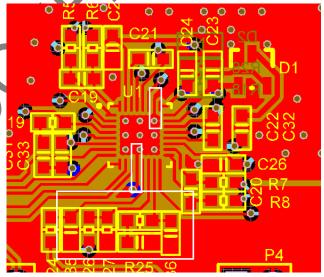

b. Layout example: put the three capacitors near IC on the top layer. Connect the capacitors to each pin on the same layer, and connect the capacitors to ground pour through vias.

Figure 8 Top layer view

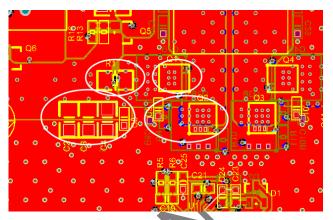

Put IBUS current sense resistor, MOSFETs and bulk capacitor at VBUS side as close as possible. And the low side MOSFET and bulk capacitors should be very close to PGND pins. Between current sense resistor and high side MOS, add a 100nF 0402 capacitor to PGND. It is helpful to suppress high frequency noise. Put it very close to MOS and PGND pins.

b. Layout example: put all these components on the top layer as a group, and the VBUS and PGND power paths should be as wide as possible. The low side MOS, 100nF capacitor and the bulk capacitors connected to PGND pins through ground pour on both top layer and bottom layer.

Figure 10 Top layer view

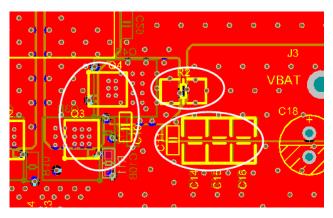

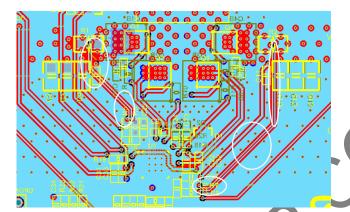

3. Put IBAT current sense resistor, MOSFETs and bulk capacitor at VBAT side as close as possible. And the low side MOSFET and bulk capacitors should be very close to PGND pins. Between current sense resistor and high side MOS, add a 100nF 0402 capacitor to PGND. It is helpful to suppress high frequency noise. Put it very close to MOS and PGND pins.

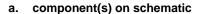

#### component(s) on schematic

Figure 11 Schematic

b. Layout example: put all these components on the top layer as a group, and the VBAT and PGND power paths should be as wide as possible. The low side MOS, 100nF capacitor and the bulk capacitors connected to PGND pins through ground pour on both top layer and bottom layer.

Figure 12 Top layer view

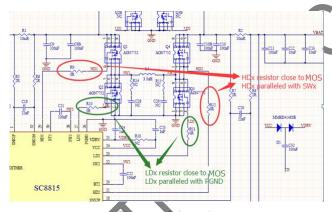

4. The driver signals (LD1 / HD1 / SW1 / LD2 / HD2 / SW2) as shown below should be routed with wide traces (≥ 15 mil). The driver resistors should be placed near MOS. The HDx and SWx should be routed in parallel, close to each other; the LDx should be routed in parallel with PGND traces (≥ 15 mil) or close to PGND pour. There should be wide space filled with PGND between LDx and HDx and also wide space from LDx to SWx to avoid interference.

Figure 13 Schematic

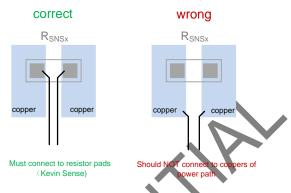

The current sense traces should be connected to the current sense resistor's pads in Kelvin sense way as below, and routed in parallel (differential routing), and add filter for each current sense near the IC.

Figure 14 Current sense

a. component(s) on schematic

Figure 15 Schematic